Hardware:Coolstream:HD1

Inhaltsverzeichnis

- 1 Allgemeines

- 2 Varianten

- 3 Revisionen

- 4 NeutrinoHD GUI

- 5 Fernbedienung

- 6 Geräteansichten

- 7 Innenleben

- 8 Weblinks

Allgemeines

Die HD1 ist der erste Receiver des Herstellers Coolstream. Da auf dem Receiver der HD-Nachfolger der beliebten GUI Neutrino zu Einsatz kommt, wird dieser auch gerne als dbox3 bezeichnet.

Folgende Eigenschaften zeichnen den HD1 aus:

- Erster HDTV-Receiver mit NeutrinoHD GUI

- Deinterlacer mit Bildausgabe bis zu 1080p

- Extrem schnelle Umschaltzeiten

Varianten

Die Coolstream HD1 wurde als Satelliten- (DVB-S/S2) und Kabel-Variante (DVB-C) angeboten. Seit Inkrafttreten der EU-Richtlinie zur maximalen Leistungsaufnahme im Standby im Januar 2010 wird die HD1 nicht mehr hergestellt. Der direkte Nachfolger, welcher die EU-Richtline erfüllt, ist das Modell "HD1 plus" (NEO).

HD1 S/C

Revisionen

Auflistung der Hardwareänderungen die an der HD1 durchgeführt wurden.

Rev.1

- Modellname: HD1 BSE (BLACK STALLION EDITION)

- Tuner: SAT

- Release:

Änderungen:

- Gehäuse in Klavierlack lackiert

- Frontblende aus härterem Acrylglas

- Bedientasten (unter Frontblende) in Silber

- Leiserer Lüfter verbaut (20dB)

Rev.2

- Modellname: HD1 C

- Tuner: Kabel (erste Kabelversion)

- Release: 25.01.2010

Änderungen:

- Gehäuse mit mehr Lüftungschlitzen

- Prozessor passiv gekühlt

- eSATAp Anschluß rückseitig (anstatt eSATA) - Dieser beinhaltet einen USB Anschluß und eine 5V Stromversorgung für externe Festplatten (2,5")

- Modemanschluß

Rev.3

Siehe Coolstream NEO

Andere

NeutrinoHD GUI

Auf der HD1 kommt NeutrinoHD als GUI zum Einsatz und ist somit der erste (und bislang einzige) HD-Receiver auf dem diese GUI verwendet wird.

Fernbedienung

Geräteansichten

Die Coolstream HD1 verfügt über diverse Anschlussmöglichkeiten. An der Frontseite befinden sich das Display, Bedientasten, Schächte für Smartcards sowie ein USB-Anschluß, an der Rückseite Anschlüsse für HDMI, Scart, eSATA (Sat) eSATAp (Kabel) und vieles mehr.

Frontseite

- Gerätedisplay 12-stellig

- Diverse Bedientasten

- USB 2.0 Anschluß

- Smartcardreader (Conax)

- 2 Common Interface (CI)-Steckplätze

Bedientasten

Erklärung der Bedientasten von links nach rechts.

| Taste | Funktion |

| POWER | Schaltet den Receiver ein bzw. aus |

| Menü | Öffnet das Hauptmenü oder geht zurück zum vorherigem Menü |

| OK | Bestätigt die Menüauswahl |

| CH+ / CH- | Programmwechsel / Menü auf/ab |

| Vol+ / Vol- | Lautstärkeregelung |

| VF | Wechselt das Videoausgabeformat unter den voreingestellten Betriebsarten (siehe NeutrinoHD Videosysteme) |

Rückseite

HD1 S

- Netzkabel (100V-230Volt / 50Hz/60Hz / 30W max.)

- Netzschalter

- SATA (Festplattenanschluss ohne Stromversorgung)

- Ethernet (RJ45 - 100MBit/Full-Duplex)

- HDMI 1.3

- S/P-DIF (Optischer Digitalausgang)

- Scart (1x TV)

- RS 232 (Serieller Anschluss)

- Stereo RCA (Cinch) Output

- Video FBAS (Cinch)

- Component (Cinch)

- LNB IN (13/18Volt / 500 mA max.)

- LNB OUT

HD1 C

- Netzkabel (100V-250Volt / 50Hz/60Hz / 45W max.)

- Netzschalter

- E-SATA-P/USB (Festplattenanschluss mit Stromversorgung)

- Ethernet (RJ45 - 100MBit/Full-Duplex)

- RJ11

- HDMI 1.3

- S/P-DIF (Optischer Digitalausgang)

- Scart (1x TV)

- RS 232 (Serieller Anschluss)

- Stereo RCA (Cinch) Output

- Video FBAS (Cinch)

- Component (Cinch)

- RF IN

- RF OUT

Innenleben

SoC Conexant/NXP/Trident CX2450x (Nevis)

Das SoC (System on Chip) stammt ursprünglich von Conexant. Nach dem Verkauf der Multimediasparte von Conexant übernahm NXP, eine Tocher von Philips, die Weiterentwicklung und Produktion des Chips. NXP wiederum verkaufte die Entwicklung kurze Zeit später an Trident. Die Herstellung des Chips erfolgt weiterhin bei NXP.

Nachfolgend die Features des SOC etwas ausführlicher:

Video Decoder MPEG-2/H.264/VC-1

- Capable of decoding an HDTV program in the following formats: MPEG-2 MP@HL, MP@ML. MP@LL, SP@ML, AVC HP@L4.1, VC-1 AP@L3 and MP@HL

- Supports decoding for picture sizes up to 1920x1080 @ 30fps; supports all ATSC, DIRECTV, DVB and SCTE formats

- Supports OpenCable HDTV constrained image output on YPrPb

- Supports Advanced DTV closed captions according to EIA-708-B

- Supports Analog closed captions per EIA-608

- Supports MPEG-1 video decoding with up-sampling and filtering of low resolution video modes to full CCIR601 picture size

- Supports 14:9, 16:9 and 20:9 image aspect ratios through pan/scan or letterboxing

- Supports 3:2 pull-down of 24fps video sequence

- Supports video trick modes for PVR applications

- Automatic error concealment

Audio Decoder

- Program decoding of MPEG-1, MPEG-2, Dolby Digital, Dolby Digital Plus, MPEG-2 AAC, MPEG-4 AAC, aacPlus and WMA encoded bit-streams

- Decodes MPEG-1 Layer I and II (MUSICAM) ISO 11172

- Supports MPEG-1 Layer 3 (MP3) decode

- Supports Windows Media Audio v.9 and WMA Pro decoding

- Supports transcoding of Dolby Digital Plus with downmix to 2-channel stereo and Dolby Digital transcode

- Supports transcoding of aacPlus with down-mix to 2-channel stereo and DTS transcode

- Stereo down-mix extraction from multi-channel MPEG-2 source

- Up to 4-bit LPCM 2-channel output in I2S or left justified serial formats

- Supports sample rates of 16, 22.05, 24, 32, 44.1, 48kHz

- Stereo 24-bit audio DAC for analog audio output

- Automatic error concealment

- A/V synchronization using PTS and STC

- 2-channel ProLogic encoded Dolby Digital down-mix output via I2S and integrated stereo audio DAC

- Single program encoded bit-stream output on S/PDIF port

CPU ARM1176EJ-S

- 736 Dhrystone 1.24 MIPS at 594MHz

- 32 kB data cache, 32 kB instruction cache

- Linux/WinCE compatible MMU

- Java support through ARMs Jazelle technology

RAM

- 384 MB DDR2-667 SDRAM

In allen Geräten kommen Chips vom Typ Hynix HY5PS1G1613CFP zum Einsatz. Insgesamt sind 3 dieser Chips mit einer Kapazität von je 128 MB verbaut.

Flash

- 32 MB NOR-Flash

Als Flash kommen entweder zwei Chips vom Typ S29GL128P (128 MBit, nur Ur-HD1) oder ein Chip vom Typ S29GL256P (256 Mbit) von Spansion (ehemals AMD) zum Einsatz. Daraus ergeben sich die 32 MB. Hardwaremäßig möglich wären maximal 256 MB (zwei Chips vom Typ S29GL01GP).

Tuner (Frontend)

DVB-S (Satellit)

Der in der SAT-Variante verbaute Tuner ist von Sharp (BS2F7VZ0169)

- Demodulator STV0903BAB

- Tunerchip STV6110A

DiSEqC

Die HD1-S unterstützt DiSEqC 1.0, 1.1, 1.2, 1.3 USALS

DVB-C (Cable/Kabel)

Der in der Kabel-Variante verbaute Tuner ist von Philips und trägt die Typenbezeichnung CU1216.

- Demodulator ??

- Tunerchip ??

DVB-T (Terrestrisch)

Eine DVB-T Variante der HD1 ist nicht vorgesehen.

HDMI-Transmitter

Ausgangsformate:

- YCrCb gemäß ITU-R BT.601 (für SD)

- YCrCb gemäß ITU-R BT.709 part 2 (EIA 770.3 / SMPTE 274M / SMPTE 296M) (für HD)

- YCrCb 4:2:2 (12 bit für Y und 12 bit für C)

- Full Range RGB (8 bit pro Kanal mit Wertebereich von 0 bis 255)

- Limited Range RGB (8 bit pro Kanal mit Wertebereichvon 16 bis 235)

Eingangsformate:

- Am Eingang bekommt und akzeptiert er ausschließlich 10-bittiges YCbCr 4:4:4 gemäß ITU-R BT.601

HINWEIS: Zum Schutz des HDMI-Transmitters kommt ausgangseitig ein Chip der Fa. CMD (California Micro Devices) vom Typ CM2020-00TR zum Einsatz.

CAM-Chip

Einen separaten Chip, der als "embedded CA-Modul" fungiert, gibt es in der HD1 nicht. Zugangskontrolle ist über Ci-Module oder - je nach Lizensierung - über die integrierten Kartenleser in Verbindung mit dem Prozessor möglich.

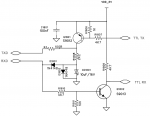

Frontprozessor

Auf der Frontpanel-Leiterplatte befindet sich der Frontprozessor (Atmel AT89C2051). Dieser kümmert sich um das VF-Display (Takterzeugung, Helligkeitsregelung, Zeichengenerator im einfachen Textmodus). Die Kommunikation zwischen CPU und Frontprozessor erfolgt über eine unidirektionale, synchrone, serielle Verbindung.

Netzwerk-Schnittstelle

Die Netzwerkschnittstelle besteht aus einem MAC (Media Access Controller), welcher integraler Bestandteil des SoC ist, und dem physikalischen Interface (PHY), welches ein einem externen Chip vom Typ IP101 untergebracht ist. Die Netzwerkschnittstelle unterstützt Datenraten von 10 Mbit/s und 100 Mbit/s sowohl im Halb- wie auch im Vollduplex.

- MAC (Media Access Controller): Conexant VMAC im SoC integriert

- PHY bzw. PLI (Physical Layer Interfae): IP101 (kompatibel zum Realtek RTL8201)

Serielle Schnittstelle COM

Folgende Einstellungen müssen zum Auslesen eines seriellen Logs am Terminalprogramm vorgenommen werden

- Datenrate: 115200 Bd

- Datenbits: 8

- Stopbits: 1

- Parität (Parity): keine

- Flußsteuerung (Handshake): keine

- Terminalemulation: Linux (ähnlich ANSI bzw. VT100)

Hinweis:Die HD1/NEO/ZEE hat eine "echte" RS232 - wenn auch im unteren zulässigen Spannungsbereich. Die Pegel liegen bei ca. +/- 4V.

Modem

Ein Modem ist in der HD1 nicht existent.